In your little bubble called the green verse lol along mister media.

We got to call you out on your blatant bullshit especially since Digital Foh dry and lens of truth were always giving the graphics nod and graphical benchmarks to ps3 exclusives. That's when Microsoft were going hard with live action trailers instead of gameplay. In each respective genre Sony was skating them....

FPS-Consensus by professionals and gamers, it wasn't even close Killzone 2/3 destroyed Halo visually.

TPS-Unchaeted 2/3 people couldn't believe what thy saw the pinnacle of graphics last Gen. Gears couldn't compete

TLOU-We won't even go there

Heavy Rain hmmmm

God of War there wasn't even any competition in tht genre

MLB the Show again no competition in exclusives

You get the point but if you do there are dozens of articles on ps3 exclusives setting the bar when all Xbox games could do was wonder how they pulled it off. If you don't believe me lol go back look at articles about Killzone and Uncharted.

Stop the blatant trolling and bs. Even towards the end multiplats were already running on par to 360 versions.

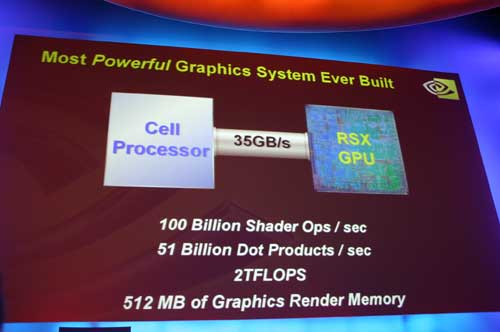

I'll drop this again just in case you want to keep lying and talking nonsense. This isn't subjective it was facts all last Gen

gamingbolt.com