HJuggernaut

Member

How many teraflops are we talking here?

The real question is how much die space Sony is willing to invest in L3 cache.If it's a choice between HBM and 3D V-cache, V-Cache wins every time.

We're at a point in real-time computing, and especially with the importance of specialized and dense data workloads like ML and raytracing, that data locality is becoming more and more important for GPU performance than ever before.

The costs of moving data around the chip are too prohibitive, and clock speeds can't be pushed much higher because the fabrication technologies are reaching physical limits and diminishing returns on cost.

Designs are starting to look more and more inwards at data locality on die, in order to see architectural improvements that can realise significant performance and efficiency improvements. We're already seeing this with Sony's work on the PS5 Pro registers and cache technologies.

The importance of ML and RT workloads next-gen will make it all the more critical to keep as much data as close to the execution cores as possible. So expanded caches and fat lower-level caches will provide orders of magnitude better performance for the majority of critical GPU workloads next-gen than any benefits HBM will provide to the main memory pool.

3D V-Cache beats HBM on bandwidth and blows it completely out of the water in terms of latency, and latency is the Achilles heel of ML performance. Having greater cache hierarchy performance overall in terms of cache sizes and bandwidth will reduce the pressure on main memory too; meaning Sony can opt for a smaller memory interface width, which reduces die size and complexity, increases yields and thus nets an overall more cost-efficient as well as energy efficient product.

Best bet for an all round solution is fanout HBM, which isn't much different to how MCD connect to the GPU with RDNA3 or StrixHalo.With the criticality of workloads like ML to next-gen, GPUs are quickly becoming so too.

Don't be looking for huge TF numbers with this PS6How many teraflops are we talking here?

I'm more interested in the CPU honestlyDon't be looking for huge TF numbers with this PS6

Its going to be a lot of AI moving forward

But the two go hand in hand because of the efficient solution they've chosen for the PS5 Pro of making it just another capability of the WGPs. The increased RT or the 300TOPs of the Pro directly correlate to the FLOPs and Half FLOPs, so to go from 300TOPs to 750TOPS, that's going to scale everything else...unless some of the TOPs and RT are inside WGPs as they currently are, and some others on the PS6 are going in an RT engine and NPU with external bridges inside the APU.Don't be looking for huge TF numbers with this PS6

Its going to be a lot of AI moving forward

I make the cost of a Pro APU ~$100 and the PS5 APU ~$50, so if the rest of the console costs $400 to manufacture, you could have 3 x Pro APUs/GPUs for $700 BoM. The GPU tiles wouldn't need a CPU, so would be smaller, but on the other hand that doesn't include the cost of the packaging technology, or the cache you mentioned. Or any other improvements.Well we know the Pro is massively overpriced and not intended to be mass mainstream sold priced product,

The BoM is estimated at $500 on selling 10m and sharing bulk component pricing with OG PS5 and Slim, and the estimate for the Pro's APU is between $180-$230, and RAM estimated is under $70, so I still don't see why they couldn't hit the $750 BoM price for launch with the spec I suggested. a memory budget over $150 and a APU budget around $400 should be enough given the product volumes expected for a OG PS6 IMO.

My estimate was that the console items, other than the memory and APU, was just $265, leaving nearly $500 for APU and memory as the volume finished prices to hit a $750 BoM which IMO is the top limit Sony would consider given they'd still maybe need to sub to $600 if sales were PS3 post launch levels.I make the cost of a Pro APU ~$100 and the PS5 APU ~$50, so if the rest of the console costs $400 to manufacture, you could have 3 x Pro APUs/GPUs for $700 BoM. The GPU tiles wouldn't need a CPU, so would be smaller, but on the other hand that doesn't include the cost of the packaging technology, or the cache you mentioned. Or any other improvements.

Edit: This isn't including the larger Pro SSD in the costing. It is also just the silicon cost paid by AMD and not including AMD's margins.

It's not, price per Gb has only increased since Vega launch and that was already sold at a loss.HBM can still be on the table.

HBM is very similar to GDDR in latency.Who told you HBM increases latency?

HBM is nothing like GDDR in terms of latency, it behaves more like regular DDR.

If it follows PS5 schedule: Q4 2025 A0 tapeout, H1 2026 1st party dev kits, H2 2026 B0 tapeout, H1 2027 3rd party dev kits, H2 2027 launch.Hey! Considering that 2025 only just started, wouldn't we be looking at a late 2026 release here? Are we even sure that this is PS6 we're talking about?

Thanks.

They can't reduce bus width due to GDDR7 density being 1.5x-2x GDDR6 at best.Or they can build a smaller chip (eg. 150 mm^2) with a 128-bit bus and rely on cache.

Really depends on the workload, AMD cancelled Turin X3D because MI300C (basically Genoa with HBM) was like 10x faster for the workloads that Microsoft was targeting.If it's a choice between HBM and 3D V-cache, V-Cache wins every time.

My guess is they can't. It will be all about RT and PSSR at $499.So how exactly do they do a console 2-3x the performance of a PS5 pro below a £750 BoM?

I would love it to be the Playstation Handheld.Hey! Considering that 2025 only just started, wouldn't we be looking at a late 2026 release here? Are we even sure that this is PS6 we're talking about?

Thanks.

LolWatch the Switch 2 faceroll this thing using DLSS 4

They went with AMD over Intel specifically so they don't break backcompat, so yes.Noob here but based on the specs, is it backwards compatible to ps5/4 games?

They went with AMD over Intel specifically so they don't break backcompat, so yes.

PS6 is design complete and in pre-si validation already, with A0 tapeout scheduled for late this year.

PS4 games will work, as long as the new UDNA GPU supports Wave64 (RDNA supports both Wave64 and Wave32).I imagine there will be PS4 games that don't work tho. I also imagine they won't bother with making PSVR2 games work either.

yes a ps6pro that can do 60fps in pro max mode on stellar blade… (can do 40fps on ps5pro)The question is, do we need a PS6

I get it now, thanks.If it follows PS5 schedule: Q4 2025 A0 tapeout, H1 2026 1st party dev kits, H2 2026 B0 tapeout, H1 2027 3rd party dev kits, H2 2027 launch.

Generations last 10+ years now. You just need to offset your mindset, most of the biggest games of PS4 came out the later half, same will happen with PS5 and 6. The cross gen period you buy the new console to enjoy much better framerates/iq.Sony releasing PS6 in late 2026 or in 2027 would make PS5 the worst Playstation generation by far. Developers have barely begun developing for this thing. Which means we'll be stuck with cross-gen titles on PS6 again for quite a long time.

We will never see a console launch now that isn't BC

It would be a super hard sell

Created using off the shelf parts to spec of the final design now they're going to put something in the oven to see how it comes out by the end of the year.

Too far along I think everyone trying to get to this crazy A.I generation in a hurryBehind the scenes its much further along than people realize

How about risc v? Is it viable?If the right technology advancements come that allow big advantages over the older consoles at a good price BC will get tossed in the wind lol especially if they can sell remakes & game streaming.

If it follows PS5 schedule: Q4 2025 A0 tapeout, H1 2026 1st party dev kits, H2 2026 B0 tapeout, H1 2027 3rd party dev kits, H2 2027 launch.

Then again we know AI/ML is RAM and bandwidth hungry and HBM is not viable in PS6… sooo, what would the option be?Really depends on the workload, AMD cancelled Turin X3D because MI300C (basically Genoa with HBM) was like 10x faster for the workloads that Microsoft was targeting.

Then again we know AI/ML is RAM and bandwidth hungry and HBM is not viable in PS6… sooo, what would the option be?

They will bump the register file on the chip, L1 and L2 caches, but spills to memory would be expensive and lots of very fast memory would burn a lot of power (I see 32 GB of RAM for PS6 with a small bump for PS6 Pro like every Pro model before).

I guess there was never a hope for an nvidia ps6

Give the Playstation 6 Steam/Epic/GoG integration with keyboard/mouse accommodation and you win the generation. Xbox ignored the idea, punish them for it.

Nintendo is already pivoting that way with the controller doubling as a mouse, it's coming. In Japan the PC market is doing very good, I think these manufacturers there are paying attention.

These consoles have essentially been PCs for like two generations now, it's mind blowing nobody capitalized on that fact. Some of the greatest games out there aren't on console, it's stupid not to include them. You can't "just" make a console anymore, it has to contend with PCs as well.

Yeah i know but imagine having a ps6 with actual state of the art tech instead of amd tech that is usually 5-10 years behindI would agree with you if Nvidia cared, but they don't..they will give their vendors the bare minimum and charged them through the roof.

I wouldn't want a crippled PS6 that cost a fortune.

You mean the tech that starts at 650€+ before it can really be used?Yeah i know but imagine having a ps6 with actual state of the art tech instead of amd tech that is usually 5-10 years behind

(At least gpu wise)

YesYou mean the tech that starts at 650€+ before it can really be used?

Yeah i know but imagine having a ps6 with actual state of the art tech instead of amd tech that is usually 5-10 years behind

(At least gpu wise)

5 years for sure, their rtx and dlss counterpart are definitely way behind, and in tech 5 years are a lot.I think you are exaggerating here a little

PS4 games will work, as long as the new UDNA GPU supports Wave64 (RDNA supports both Wave64 and Wave32).

CPU shouldn't be an issue thanks to x86-64, even if they switched to Intel (not gonna happen, but anyway).

PSVR2 games should work, as long as PS5 BC works.

There will still be games that will break for one reason or another and won't be fixed.

6 games only (they used to be more back in 2020) and these could be patched if devs wanted so...PS4 only games

While the majority of PS4 games are playable on PS5 consoles, below is a list of PS4 games that are playable on PS4 only. On PlayStation™Store, PS4 games that are not playable on the PS5 console will be marked with 'Playable on: PS4 only'.

Afro Samurai 2 Revenge of Kuma Volume One

Just Deal With It!

Robinson: The Journey

We Sing

Hitman Go: Definitive Edition

Shadwen

This list is subject to change and excludes demos, media, and non-game applications.

If PS/XBOX integrate 3rd party ecosystems, you realize they're going to lose tons of royalties (30% cut) from PS/MS store, right?Give the Playstation 6 Steam/Epic/GoG integration with keyboard/mouse accommodation and you win the generation. Xbox ignored the idea, punish them for it.

Nintendo is already pivoting that way with the controller doubling as a mouse, it's coming. In Japan the PC market is doing very good, I think these manufacturers there are paying attention.

These consoles have essentially been PCs for like two generations now, it's mind blowing nobody capitalized on that fact. Some of the greatest games out there aren't on console, it's stupid not to include them. You can't "just" make a console anymore, it has to contend with PCs as well. If the executives at Playstation want to make yet another discreet system like the PS4 and PS5, fire the lot of them, they're walled garden console brained morons, pivot towards innovation and growth instead.

Honestly, this is as ridiculous as saying you're gonna visit a restaurant with food/drinks you bought from Costco...PC is a platform where once you buy the hardware from the manufacturer, they never see any money from you again because you are buying your software from Steam, Epic and GOG.

PlayStation needs to differentiate themselves from PC, not become the same thing.

They get nothing out of making cheap subsidized/break even consoles for the world to play other store's games on. If you just want to buy a hardware to play Steam stuff they don't even want you as a customer using up a PlayStation they had to make as a free service to you.

Have a look at OG XBOX...Yeah i know but imagine having a ps6 with actual state of the art tech instead of amd tech that is usually 5-10 years behind

(At least gpu wise)

I already have a powerfull pc but if i don't wanna wait 1-2 years for every sony exclusive, i'm forced to play them on console.Have a look at OG XBOX...

It had a state-of-the-art GeForce 3 GPU, but nVidia refused to offer price drops, despite the die shrinks (we had LOTS of them back in the early 2000s), so Microsoft abandoned them real quick.

If you want the best of the best, it's best to build a PC and stop begging console manufacturers to do something they're not even interested in doing.

good info here

It seems 32GB RAM is out of the question (not possible to divide 32GB with 3GB), but 24GB is a possibility with 256-bit bus. Each new console generation will offer even smaller memory increase (no longer 16x increases like the PS3/4 did).

Don't forget the hidden second GPU in the powerbrick for the dock.Watch the Switch 2 faceroll this thing using DLSS 4

Let's hope they'll stick to 256-bit, because there's always a possibility of downgrading the bus to 192-bit (like nVidia did with Ampere -> Ada) and only offer 18GB RAM for next-gen machines.If Nvidia and AMD don't put HBM on a $1000+ GPU then I simply don't see it happening on a console anytime soon. Costs haven't really come down and GDDR7 can provide 1TB/s+ worth of bandwidth on a 256bit bus anyway. It would cheaper just to up the bus width to 384bit if they desperately need bandwidth for the next generation, but I don't think that will happen either.

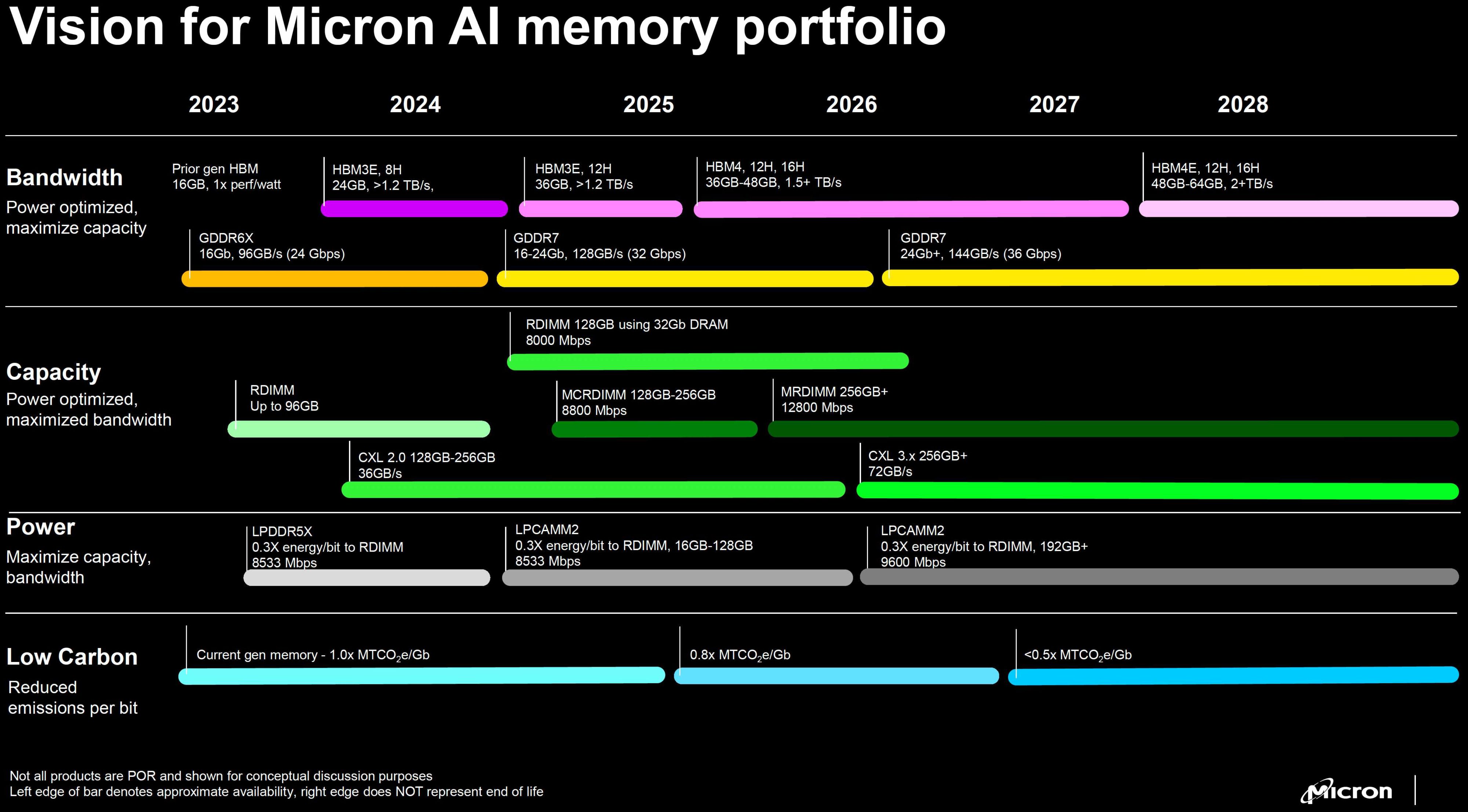

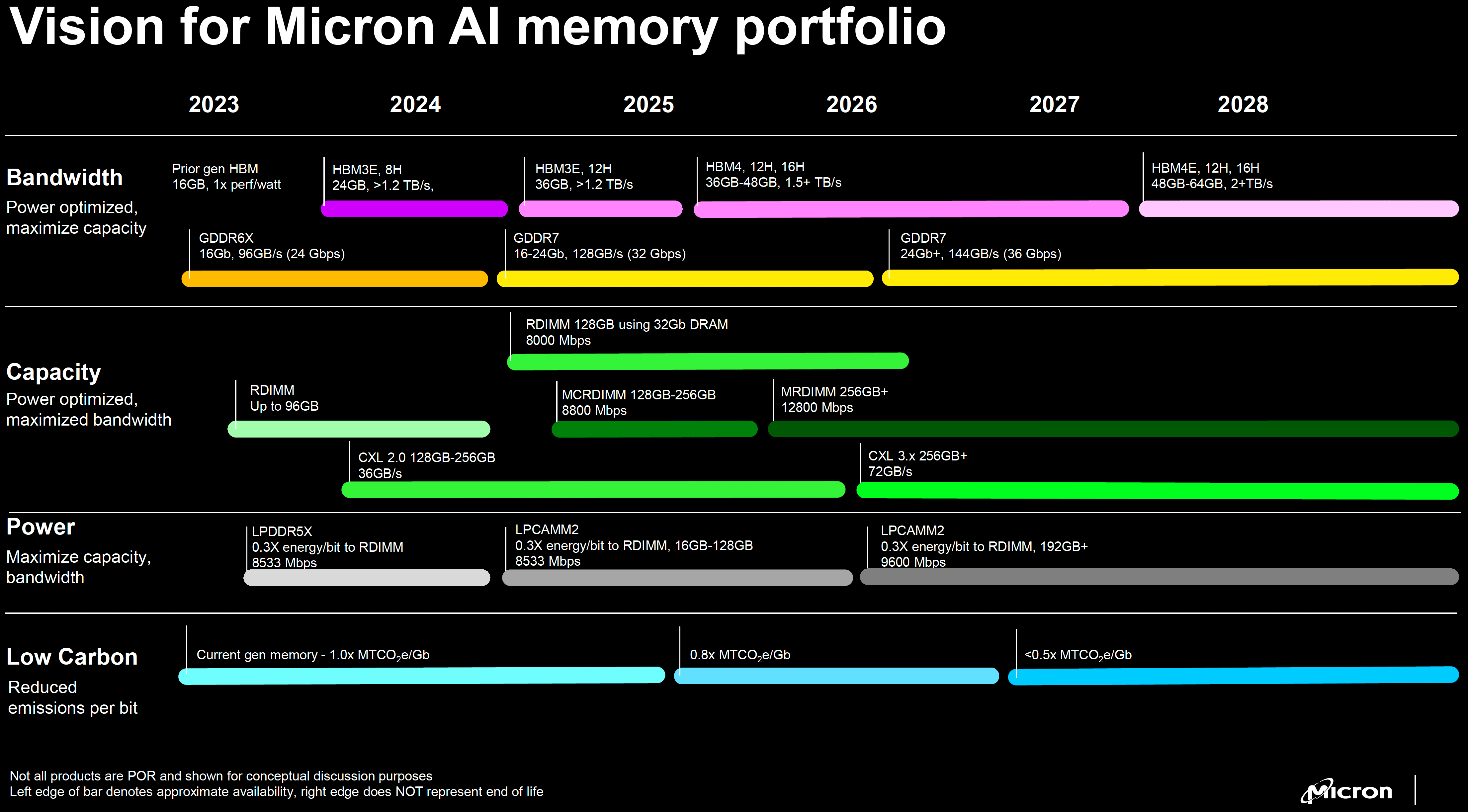

24GB at 36Gbps for the PS6 seems very likely at this point.

I don't see it in the roadmap, unless you're talking about delaying next-gen consoles to 2030 (I would be fine with that).4 GB chips might be available by then.