ap_puff

Banned

That's why I said 5nm + 2nm chiplets.

Having half the chip on 2nm is cheaper than having the whole chip on 2nm.

I don't think the AI bloom would affect Sony tbh. Sony would be ordering 100+ chips, TSMC isn't going to panic, not one bit.

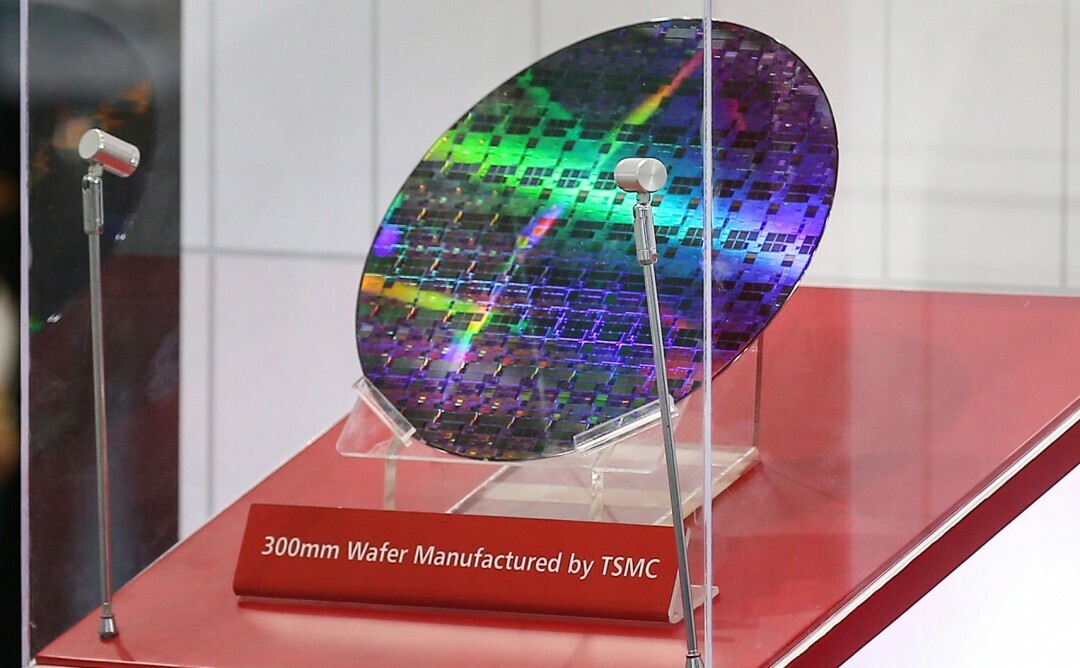

TSMC to Raise Wafer Prices by 10% in 2025, Customers Seemingly Agree

Taiwanese semiconductor giant TSMC is reportedly planning to increase its wafer prices by up to 10% in 2025, according to a Morgan Stanley note cited by investor Eric Jhonsa. The move comes as demand for cutting-edge processors in smartphones, PCs, AI accelerators, and HPC continues to surge...

"However, TSMC is signaling potential shortages in leading-edge capacity to encourage customers to secure their allocations. Adding to the industry's challenges, advanced chip-on-wafer-on-substrate (CoWoS) packaging prices are expected to rise by 20% over the next two years, following previous increases in 2022 and 2023. TSMC aims to boost its gross margin to 53-54% by 2025, anticipating that customers will absorb these additional costs. The impact of these price hikes on end-user products remains uncertain."

Even the 5nm node is getting more expensive rather than trending downward