Geometric-Crusher

"Nintendo games are like indies, and worth at most $19" 🤡

edit

Last edited:

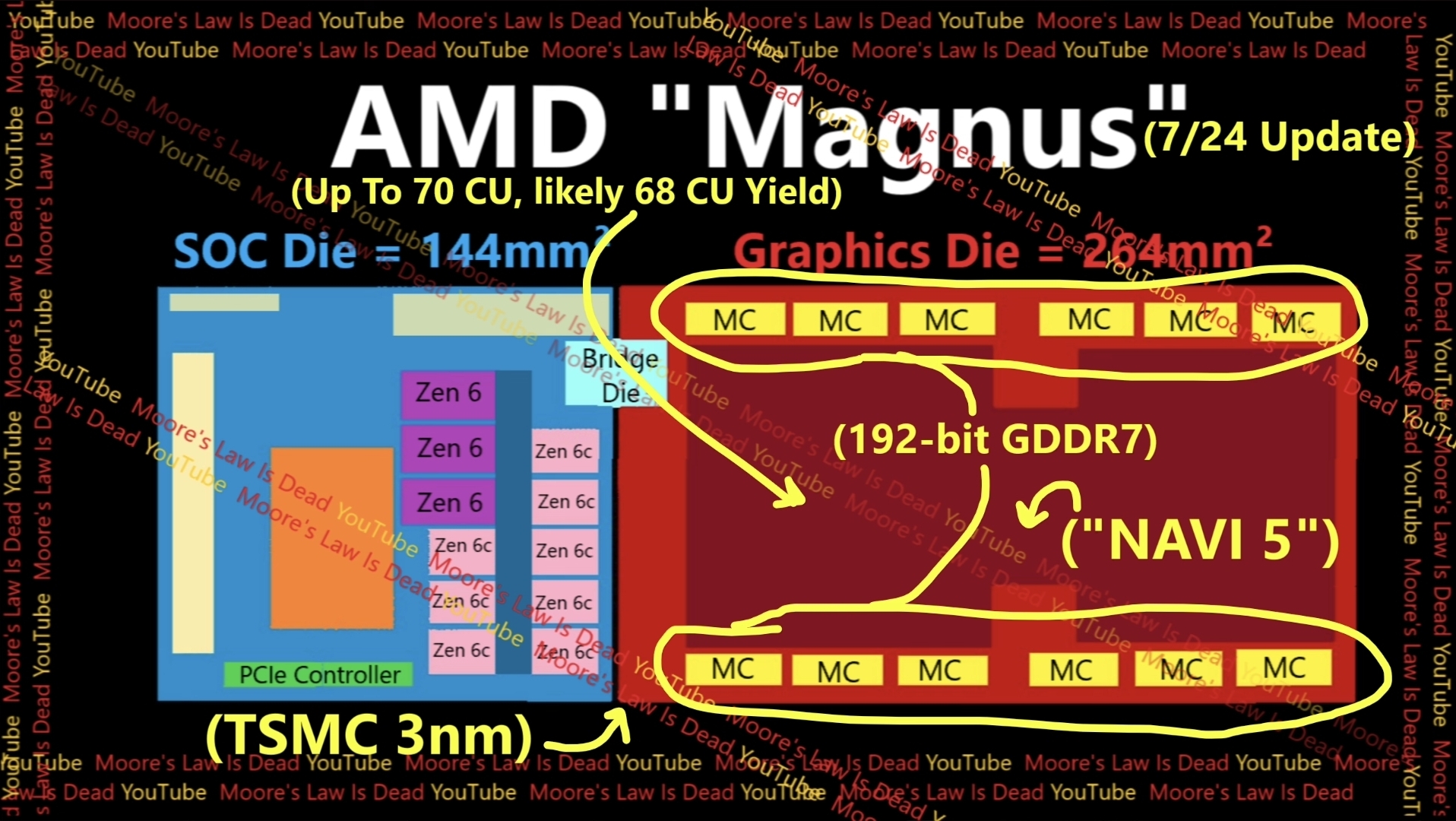

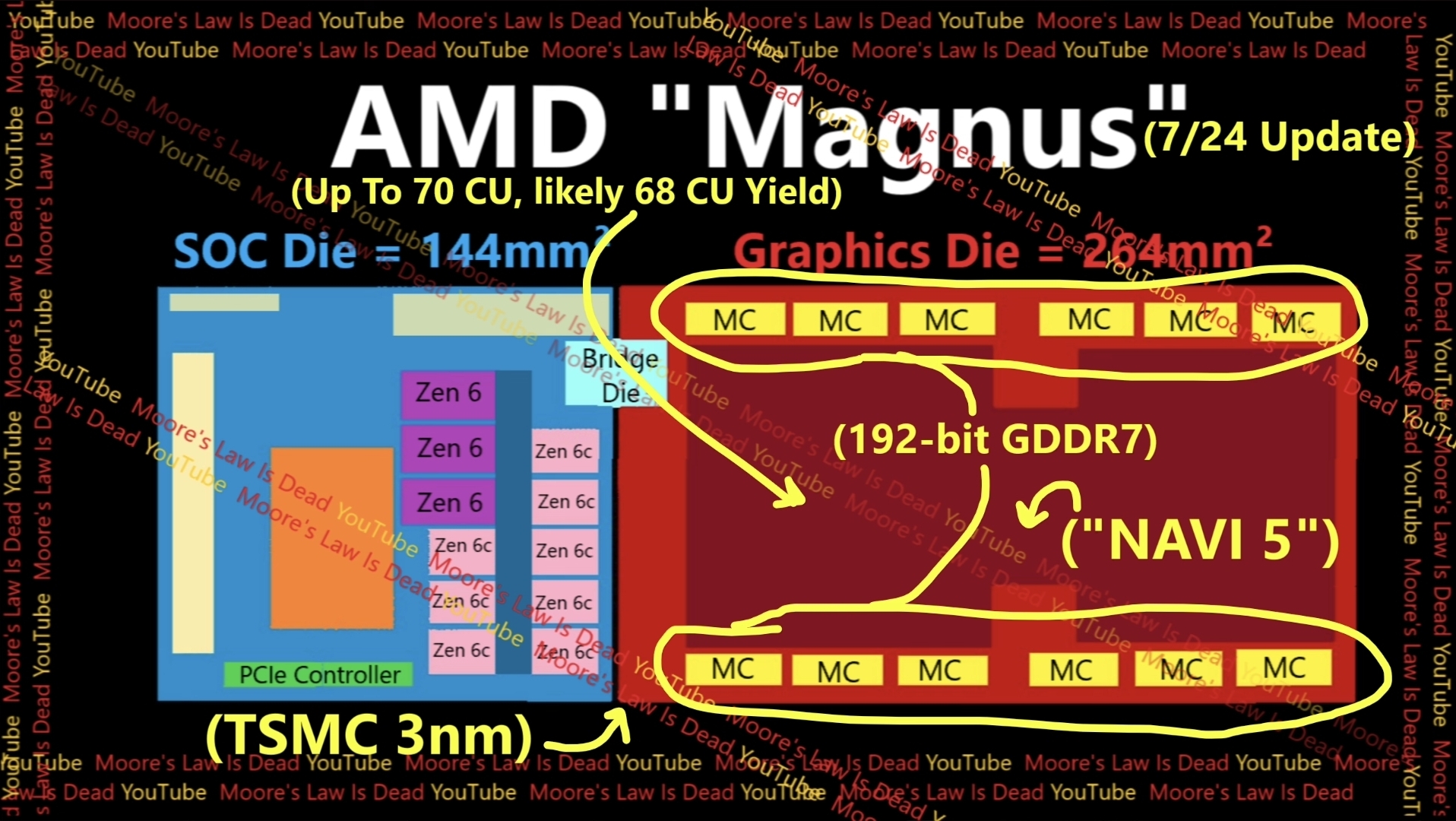

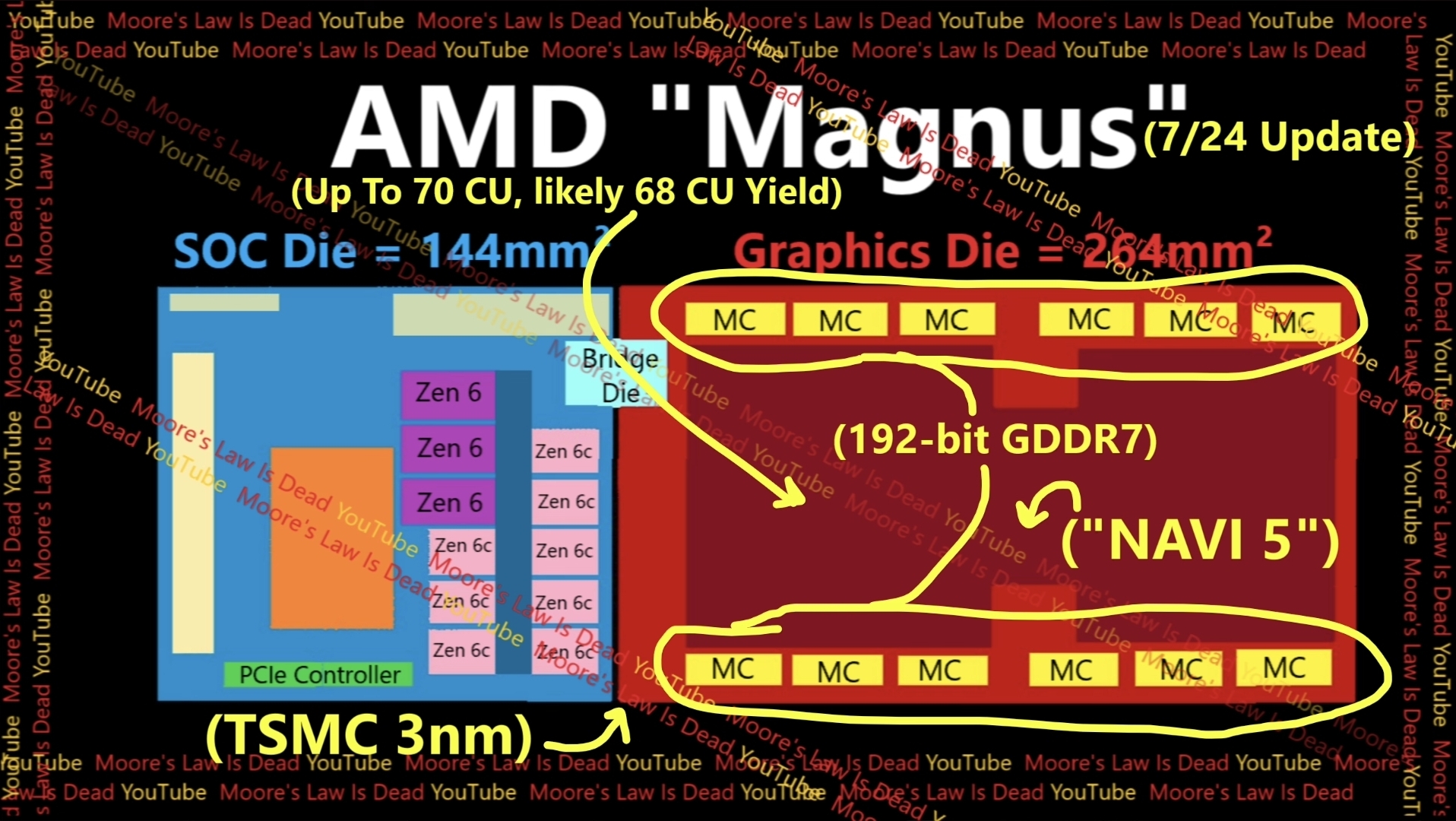

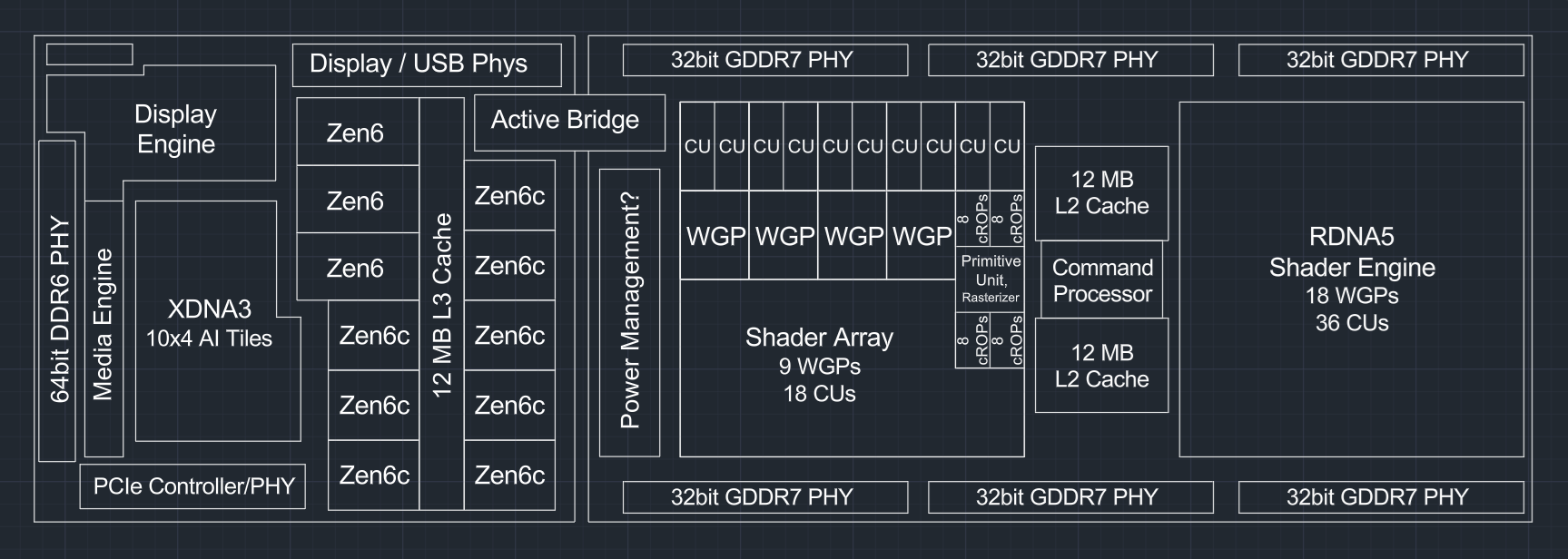

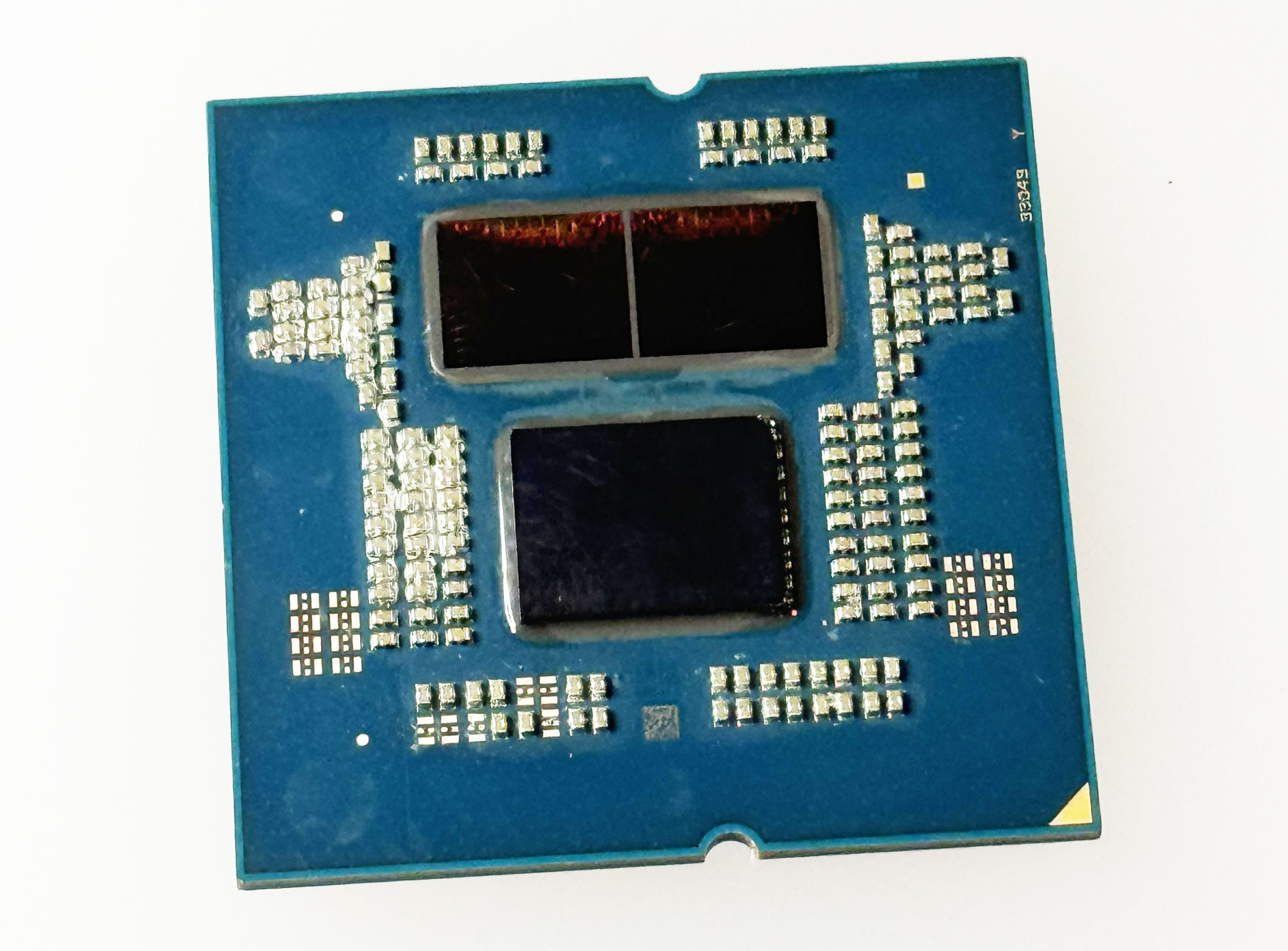

Keep in mind Magnus is a Chiplet design.

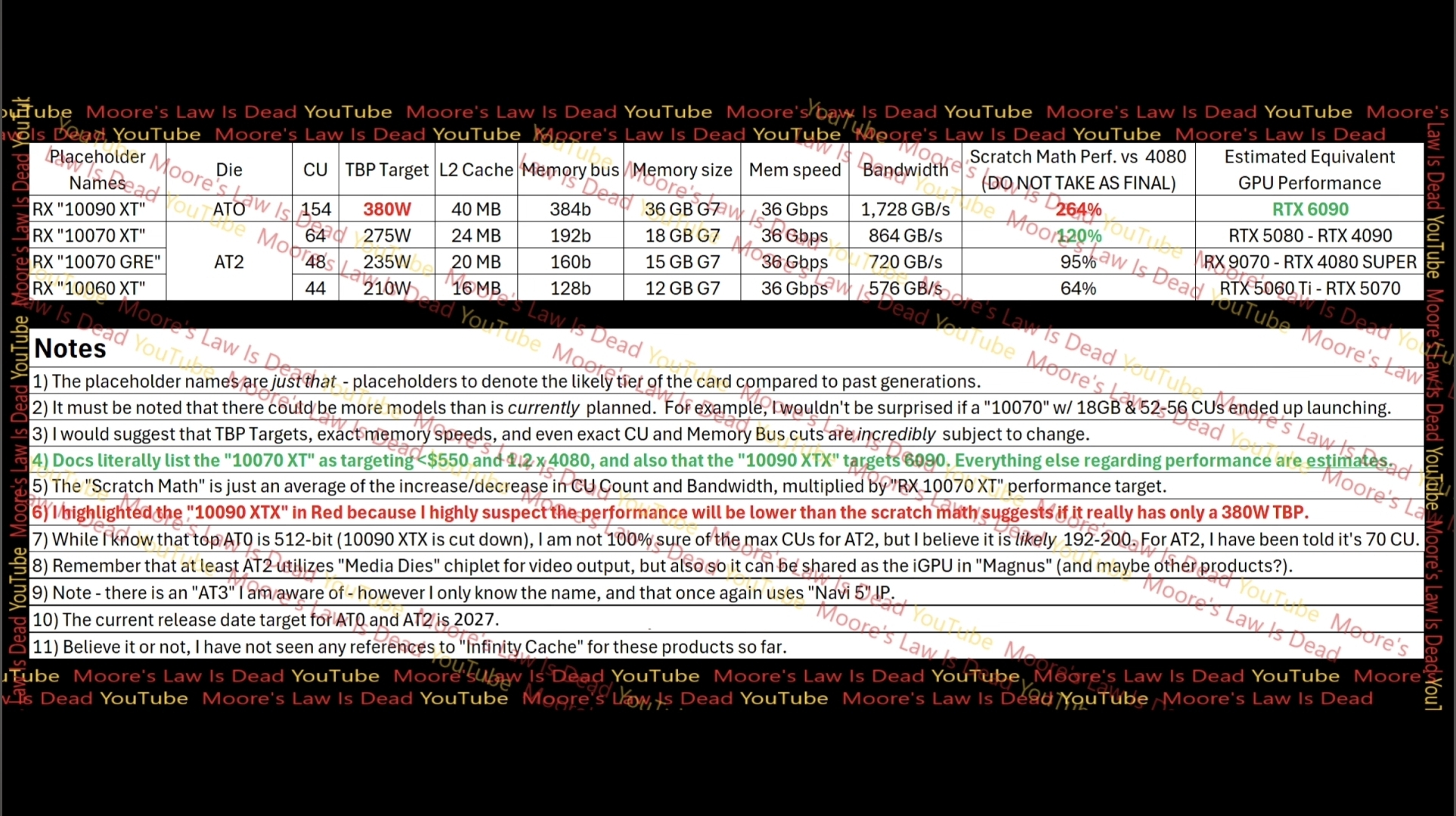

MLiD says the GCD will be used as a desktop GPU with a Media Die attached to it.

Remember that at least AT2 utilizes "Media Dies" chiplet for video output, but also so it can be shared as the iGPU in "Magnus" (and maybe other products?).

Makes sense. If they can match the power draw of Z2X in the Xbox Ally which has 16 CUs, I guess it could work with the chiplet design. Point was, they have to have at least one other configuration.Why does it need to be a variant when you can combine one of a few Zen 6 discrete CPU consumer products and most of not all of the RDNA5 GPUs together via the advanced packaging solution.

I'm not sure if ALL AMD discrete GPUs will have BC. For example, I don't think if an AMD GPU paired up with Intel CPU will have Xbox Console BC.Because Magnus is a package of discrete off the shelf AMD Zen6 CPU and discrete off the shelf RDNA 5 GPU. It's the mid-range / Series X successor.

Xbox won't have a bespoke CPU nor GPU that will not be able to be bought individually of the market in AMD consumer GPUs. All discrete AMD RDNA5 gaming GPUs (only two configurations really) and future GPUs will have Xbox BC and all will have the latch for a bridge die.

Specs:

11 Core Zen 6.

68 CUs at 2.5-3GHZ

18GB GDDR7 on 192 bit bus, 896GB/s.

8-16GB DDR5 on 128 bit bus, 70-100GB/s

Upscaling on the NPU isn't viable.

It's outside the graphics pipeline and is only 50 TOPs, while RDNA4 has upto 1557 TOPs.

The NPU would be most likely used by Copilot as an AI assistant.

Each major step since N7 roughly doubles the price while the advantages in density and clocks on everything past N5 are +50% at best combined.The estimated per wafer prices for N5 and N3 are in the $17k - $20k range. So likely the price per transistor is similar. It's N2 that sees the huge price jump.

Moore's Law has slowed down significantly but it's not that bad, N2 is +300% density, +50% fmax and -80% power vs N7 at +200% price.Each major step since N7 roughly doubles the price while the advantages in density and clocks on everything past N5 are +50% at best combined.

It's all on N3P.I'll be very surprised if next gen consoles will launch on anything but N4.

LOL no, it +30% at best and will likely be closer to +15% for mixed HP logic and memory. That's against N3P. What's the point in comparing with N7?N2 is +300% density

The rumoured price for N5 was ~$17k per wafer, compared with ~$10k for N6/7.Each major step since N7 roughly doubles the price while the advantages in density and clocks on everything past N5 are +50% at best combined.

You're not getting anything out of these new processes aside from the ability to make a huge and expensive as fuck chip - which can only be used in DC space or by Apple since they had like 80% margins on their A chips previously.

N2 is just more of that on top of what we've seen with N7, N5 and N3 already with an added "bonus" in the form of completely lackluster density gains.

I'll be very surprised if next gen consoles will launch on anything but N4. Or, well, they could wait till 2030 I guess.

I guess they could use the GCD for discrete GPUs. But that Magnus will also need that Media Die for AV1 hardware encoders and decoders in order to be used for xCloud.

It would be better to use FSR3 with the Xbox Ally imo. With Magnus though, the GPU being based on RDNA5 is more than capable for upscaling, utilising it's 3rd gen AI Accelerator for FSR5.Qualcomm Snapdragon X Plus and X Elite devices used Auto SR for upscaling after doing the x64 to ARM64 code translation in real time. Those devices all have NPUs with 50 TOPs.

The leaked Xbox slide also mentioned use of Auto SR. So the NPU will be good enough to do upscaling to at least 1080/60. It's more likely for use on the handhelds and laptops like the Xbox Ally with Z2X includes the NPU.

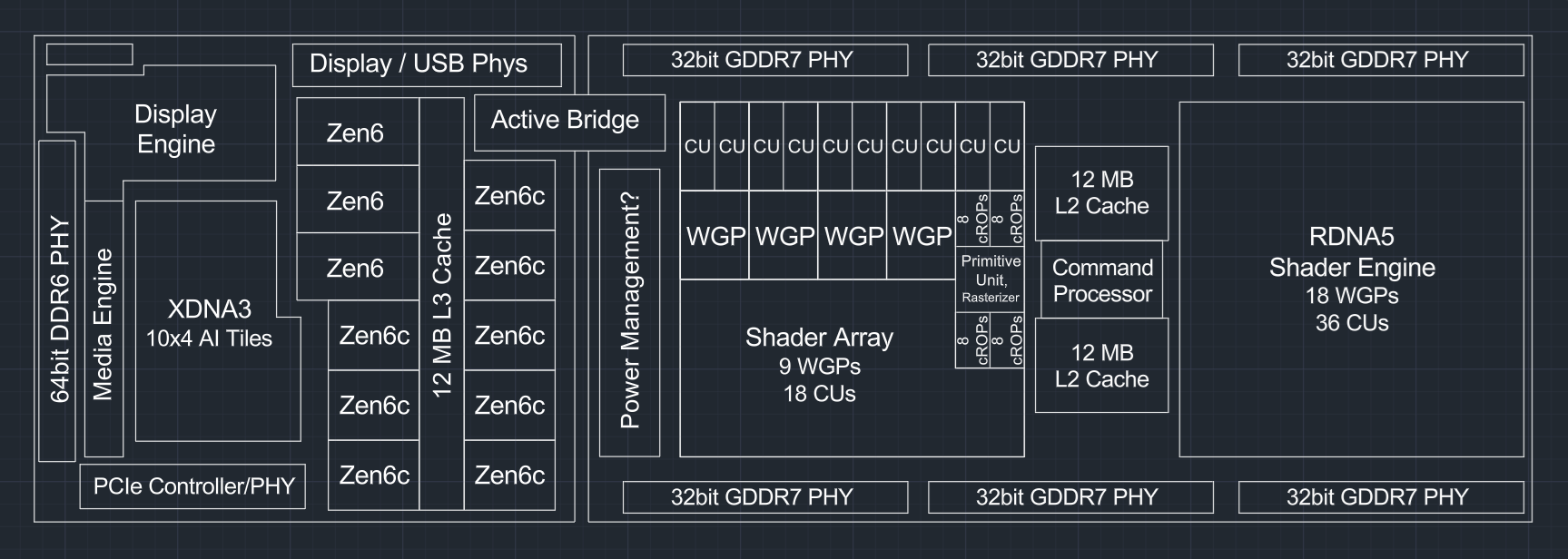

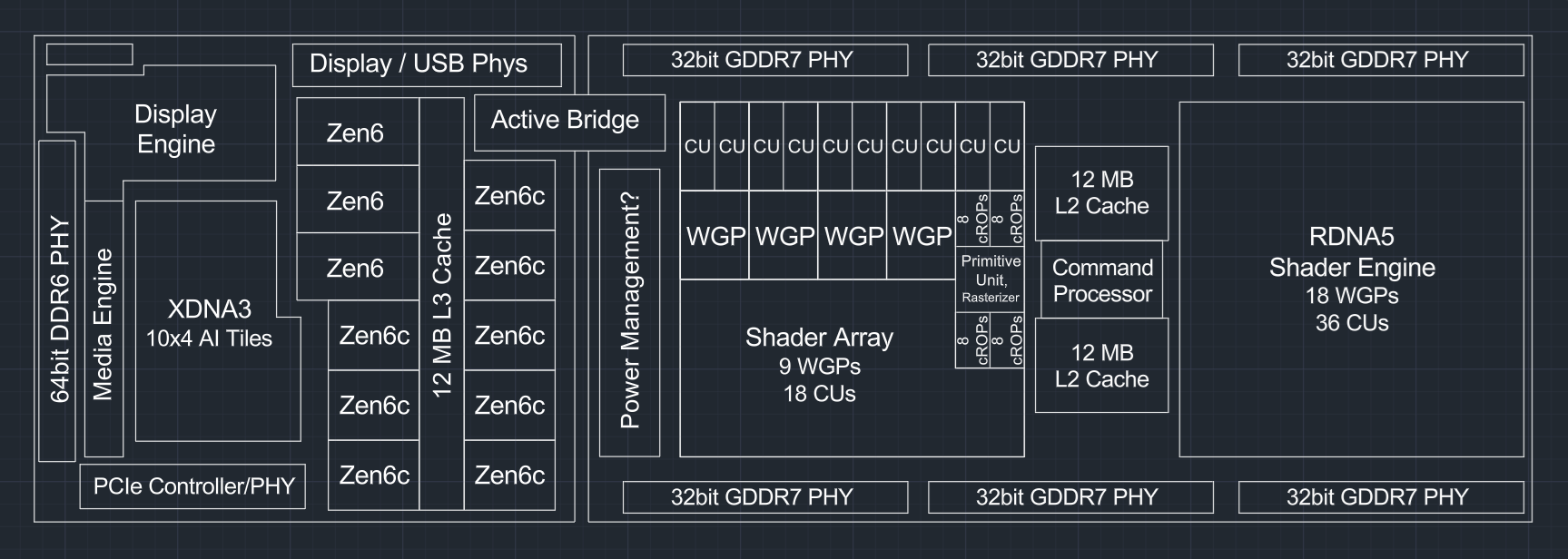

It's 192-Bit (each MC is 16bit) and 64-128-Bit DDR is speculated to be in the SoC die, like this.

Why 192 bit?

"MC" nomally means "Memory Controller" but since a GDDR Memory Controller typically handle 2 channels I suspect "MC" in this case means "Memory Channel".

That gives us 12 memory channels. Each channel is 32 bit giving us a total bus width of 12×32=384 bits.

Or maybe the sketch just sucks...

Ohh, I see. "MC" refers to 16 bit sub-channels.It's 192-Bit (each MC is 16bit) and 64-128-Bit DDR is speculated to be in the SoC die, like this.

Which is a representation I did based on what I think it may look like. As more info becomes available, I'll update it.

Correct.Ohh, I see. "MC" refers to 16 bit sub-channels.

Very confusing to call them "MC" though.

Edit: And we are expecting the console to actually use the DDR interface? I.e. we could end up with a 16GB DDR5 + 18GB GDDR7 solution?

Yeah.Correct.

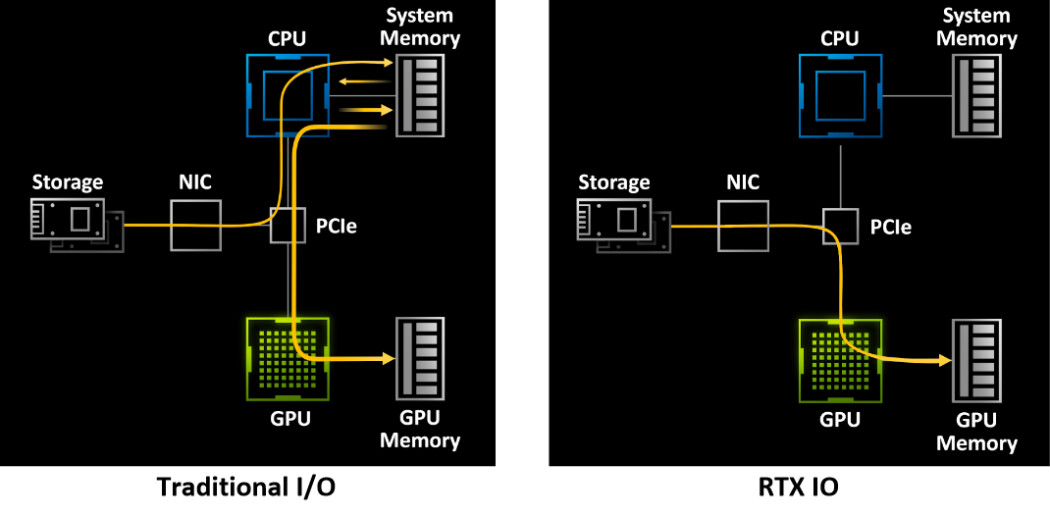

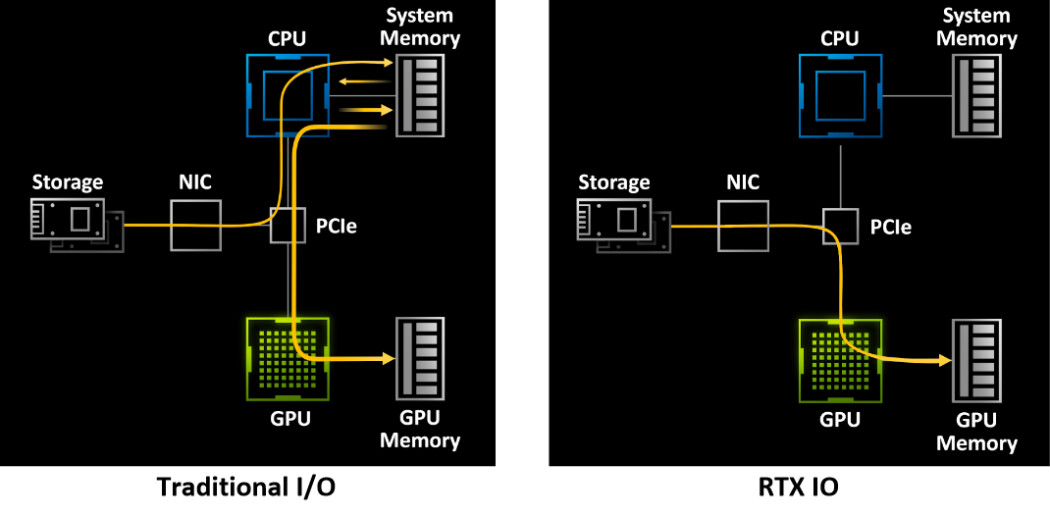

RTX IO or DirectStorage is how I see it working.

Yeah.

Looking forward to play Excel on this hardware then.

Edit: The good bit is that CPU is no longer handicapped by GDDR latency.

It's 192-Bit (each MC is 16bit) and 64-128-Bit DDR is speculated to be in the SoC die, like this.

Which is a representation I did based on what I think it may look like. As more info becomes available, I'll update it.

I don't see why there would be parity rules.If there's parity rules regarding game modes then that handheld is sure gonna hinder the gangbuster games. Simple resolution scaling doesn't work anymore.

The SoC is a custom design and the DDR would most likely be embedded just like how the GDDR7 would be embedded.I think it's most likely dual channel DDR as the CPU die will be in consumer desktop CPUs. Are there even single channel CPUs on the market?

It's a unified memory architecture - unless inference has to specifically pass something to a shader, you are just reading/writing the memory same way you would either way.Upscaling on the NPU isn't viable.

It's outside the graphics pipeline and is only 50 TOPs, while RDNA4 has upto 1557 TOPs.

The SoC is a custom design and the DDR would most likely be embedded just like how the GDDR7 would be embedded.

We are talking about Magnus right?It's a unified memory architecture - unless inference has to specifically pass something to a shader, you are just reading/writing the memory same way you would either way.

Worst case you have +1 indirection at the end.

The TOPs need to be in context - this would be targeting 1080p upscales (like Switch 2 for most part) so there's substantially less work to do - and PS5Pro does 4k with 300TOPs, and is getting some version of FSR4 on that.

Pretty sure that would required a new socket.Of course the DDR will be embedded. Doesn't mean the CPU die can't be sold separately as a discrete CPU on the market.

Maybe I misread, the 50 TOPs NPU part has only been on mobile APUs so far.We are talking about Magnus right?

Why use the NPU for upscaling, which is on a different die, when the GPU is already more than capable?

Pretty sure that would required a new socket.

Unified architecture with both DDR5 and GDDR7 memory?It's a unified memory architecture

Unified architecture with both DDR5 and GDDR7 memory?